高速信号の遅延チューニングの予備知識

オシロスコープに表示された2つの信号を見てみましょう。信号トレース間の長さ/タイミングの不一致により、下流のゲートが不適切にトリガーされる様子がわかります。マスタークロック信号の移動時間と、異なるコンピューター インターフェースでの送受信データの往復時間に着目すると、状況はなお悪くなります。SDRAMは、スレーブデバイスにクロックを配置し、取得したデータとともにクロック信号を送信することで、これをうまく解決しました。一方、他のインターフェース (USB 3.0、SATAなど) はデータから直接、クロック信号を抽出します。

それ以外の場合は、複数の並列相互接続間の遅延チューニング、差動ペアでの配線、およびクロック信号の使用により、データが確実に適切なタイミングで適切な場所に届くようにします。どのような配線長のチューニング方法を適用する場合も、単純な長さだけでなく、さまざまな信号/インターフェースの規格で信号遅延時間を処理する必要があります。ここでは、遅延チューニングの設計と継続的な信号の同期化についてあらかじめ知っておくべき事項を説明します。

遅延チューニングと配線長チューニング

配線長チューニングと遅延チューニングは、基本的には同じ考え方を指します。目標は、一致するネットグループの信号トレースの長さを同じ値に設定することです。これは、制約されたタイミングのずれの範囲内ですべての信号が到達するための考え方です。一致するネットグループ内で2つの信号トレースが一致しない場合、信号を同期する通常の方法は、短い方の信号トレースに蛇行を追加して遅延を増やすことです。トロンボーン、ノコギリ歯、アコーディオンなどの形状の蛇行は、トレースに遅延を加える典型的な方法です。

クロック信号と複数の信号線の間、差動ペア内、またはクロック線がない複数の差動ペア間のいずれに遅延チューニングを適用する場合も、信号に固有のタイミング許容差を把握している必要があります。差動ペアレシーバーとSerDesチャンネル内のコンポーネントでは、各信号間で許容される配線長の不一致を決定する制限要素は、相互接続における信号立ち上がり時間と伝搬遅延です。

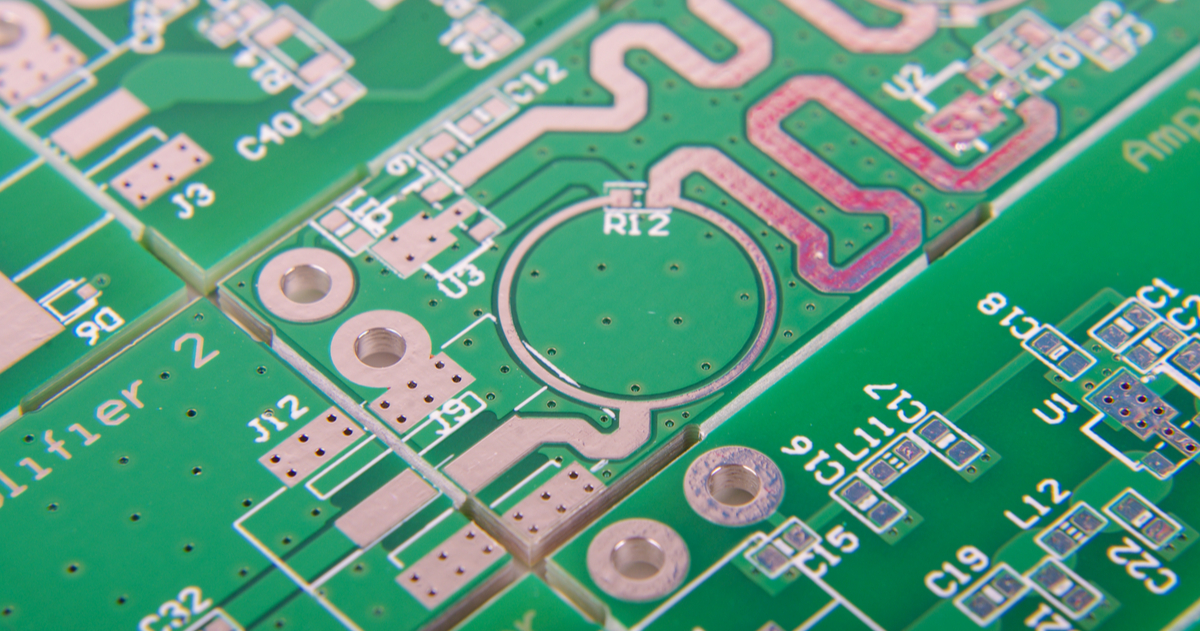

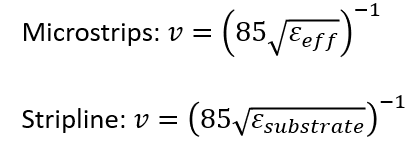

異なるデータ速度で動作し、異なる信号規格で動作する各インターフェースは、許容される配線長、またはタイミングの不一致の値が異なります。これらの値は通常、FR4での作業を前提としますが、異なる比誘電率を持つ基層上のより特殊な設計では、配線長の不一致の制約が異なります。基板内のI/Oチャネルを計画する際、基板で許容される配線長の不一致の値を調べ、この許容される不一致をタイミングの不一致に変換する必要があります (以下の式を参照)。

タイミングの不一致の処理

遅延チューニングで中心となる考えは、配線長の不一致ではなくタイミングの不一致を処理することです。配線長の不一致のみを考慮するPCB設計ソフトウェアを使用している場合は、特定の基層の正確な配線長の不一致を計算する必要があります。配線長の不一致は、特定の基層の信号速度 (単位はin./ps) によって算出されるタイミングの不一致に相当します。

一般に、比誘電率が大きい基層は信号速度が低下し、2つの信号間で許容される配線長の不一致が大きくなります。同様に、標準コンポーネントをオーバードライブしていると、立ち上がり時間が短くなり (スルーレートが高くなる)、タイミングの制約も厳しくなります。1次近似に対して、信号の立ち上がり時間を半分にした場合、許容されるタイミングの制約も半分にする必要があります。

許容される不一致は通常、立ち上がり時間ではなく、クロック期間の許容差に関して定義されます。特定のクロック期間において、許容される配線長の不一致は、信号速度に反比例します。想定される比誘電率(例えばFR4)で長さの不一致を見積もっている場合、特定の基層材質の信号速度を使用して配線長の不一致を変換する必要があります 。

差動ペアの位相不一致

「位相不一致」という語は、配線長チューニングや遅延チューニングと同じ次元でたびたび用いられますが、差動ペアを扱う場合、重要な結果をもたらします。差動ペアが特殊な配置のビアを配線する必要がある場合など、差動ペアの配線では、ペアの両端に結合されていない短い領域が生じることがあります。これは、ペア全体の長さの不一致に加えて発生する可能性があります。場合によっては、一致したグループ内の複数のペアも長さが一致する必要があります。

位相を一致させるには、一致しない端に少量の銅箔を追加する必要があります。これにより、結合されていない部分の配線の長さが一致します。これは、差動ペアが同相モードノイズを必ず適切に抑制できるようにするためにかなり重要です。非結合部分で発生する同相モードノイズは、レシーバーに到達した後も両方のペアで必ず一致するよう、同じ距離を伝搬する必要があります。

非結合領域で位相が一致したら、差動ペアの残り部分の長さが一致していることを確認する必要があります。ただし、最初に適切に配線されている場合は、ペア全体にわたって長さが一致している必要があります。差動ペアに配線長を一致させる部分を追加して、ペア間のスキューを補正する場合は、差動ペアの全体にわたって、その部分を対称に配置する必要があります。同相モードノイズを十分に抑制し、信号を抽出するため、ペア間のスキュー制約は通常、ペア間のスキュー値よりも緩やかであることに注意してください。

遅延チューニングの詳細: ピンパッケージ効果

信号は、特定コンポーネントのピン/パッドに到達後、露出した導体を通り、ボンドワイヤに沿ってパッケージの内部、そしてパッケージ ダイに入る必要があります。露出した導体、パッド/ピン、および内部回路への入力には寄生インダクタンスと静電容量があり、信号は、信号トレースでの移動と比較すると、ボンドワイヤの通過時と異なる速度で移動します。また、ボンドワイヤには若干異なるジオメトリーがあり、異なるピン上の信号に、異なる遅延レベルが追加されます。

どこのデバイスメーカーも、特定のコンポーネントのピンパッケージの遅延を公開しているはずです。これは、ps単位の遅延、または長さ (通常はmm、またはマイクロメートル) で表されます。この遅延値は、各コンポーネントのIBIS 6のマニュアルから入手できます。この長さは、差動ペアにおいて、あるいは複数の同期差動/シングルエンド信号に対して、信号を使って任意のタイプの遅延/配線長チューニングを行う場合に必要です。

対話型の効果的な配線、およびレイアウト後の解析ツールAltium Designer®により、統一されたルール駆動設計エンジンの上に構築された完全なパッケージが実現され、高速信号の遅延チューニングと重要なシグナルインテグリティーのシミュレーションを実装できます。また、回路図の作成、コンポーネント管理、製造業者向けの出力を準備するためのツールも用意されています。

今すぐ基板設計CADのAltium Designerの無料評価版をダウンロードし、業界最高のレイアウト、シミュレーション、および製造計画ツールの詳細を学習できます。詳細は、今すぐアルティウムの専門家にお問い合わせください。